책 범위 : 15) Memory의 선정과 XIP ~ 18)일반적인 CPU 동작 예(CORE)와 Pipe Line

memory 선정과 xip

임베디드 시스템에서 메모리 선정은 기본적인 시스템 구성과 성능에 가장 큰 영향력을 행사

메모리 종류 선정을 어떻게 했느냐에 따라 memory map을 어떻게 구성할 것인지 디자인 가이드가 달라진다.

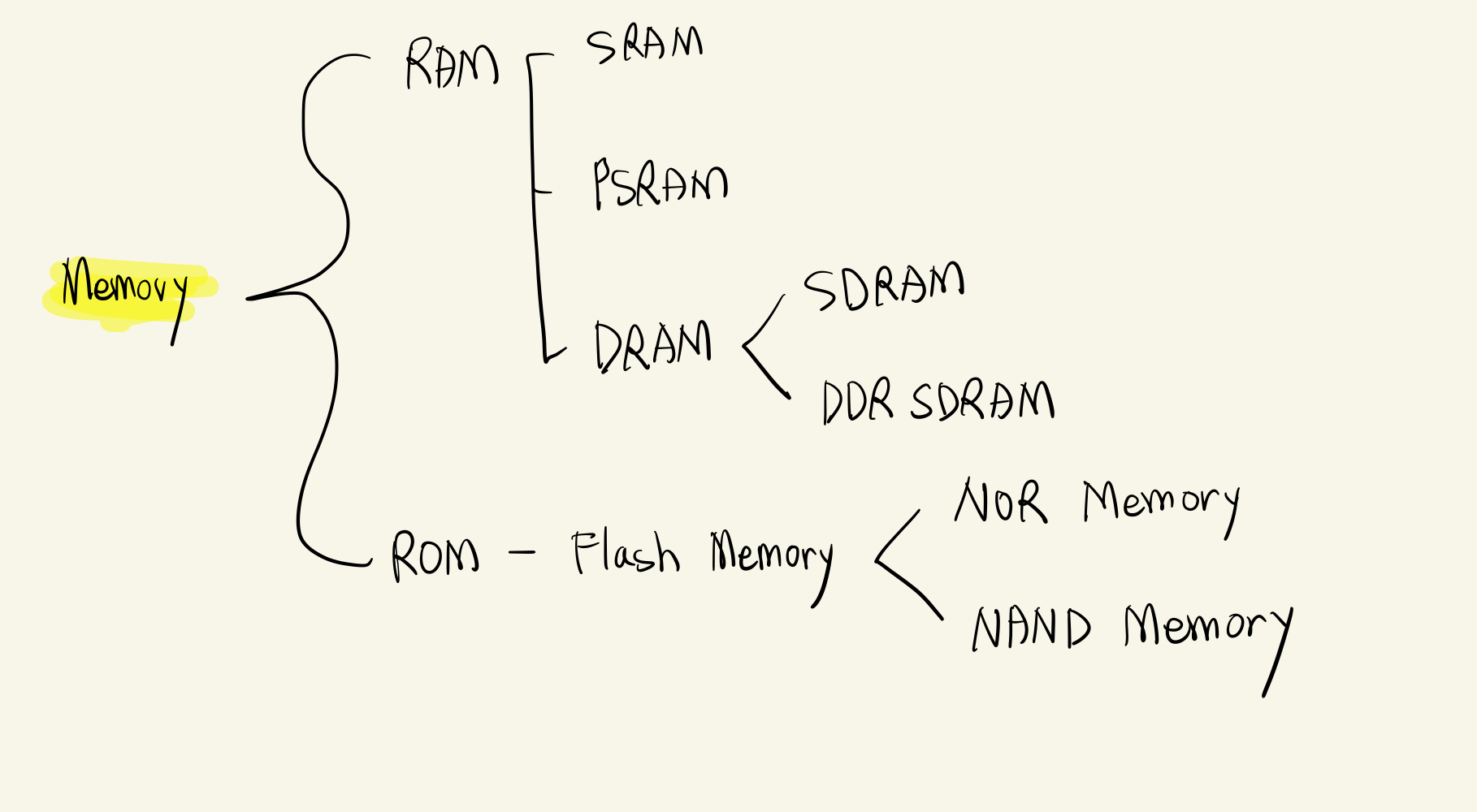

메모리는 크게 RAM(휘발성)과 ROM(비휘발성)으로 나뉜다.

예전에는 RAM에는 데이터가, ROM에는 Code가 들어가는 것이 통상적인 예

XIP(execute in place)

= XIP는 메모리 상에서 직접 프로그램/코드를 실행할 수 있는 기술

= Word 단위의 Access가 가능하여, SW를 Execution 할 수 있는 것을 XIP

기본조건으로는 Random Access가 가능해야 한다. = Byte, Word 등의 크기를 직접 Access 가능해야 한다.

모든 RAM은 이런 요건을 충족한다. 즉, RAM에 프로그램/execution 이미지를 올리기만 하면 실행 가능하다는 말

RAM 성능

- SRAM

가장 비싼 RAM은 SRAM(Static RAM)

아무런 전기적 컨트롤 없이 그저 우리가 생각하는 Random Access가 가능한 휘발성 메모리기 때문

- DRAM

제일 싼 RAM은 DRAM(Dynamic RAM)

DRAM은 한번 메모리 셀에 기억 시킨다고 끝나는 것이 아니라, 시간이 지나면 Data가 유실된다.

그래서 일정 시간마다 다시 전하를 충전해 줘야 자기가 갖고 있는 데이터를 잊어버리지 않고 계속 간직한다.

= DRAM은 Charging을 위한 precharge circuit을 가지고 있어야 한다.

- PSRAM

PSRAM은 Pseudo SRAM으로 DRAM과 SRAM의 장점을 본 따서 만든 RAM

컨트롤 할 필요 없는 DRAM, HW적으로 precharge 해주는 회로가 DRAM에 딸려 나온다.

ROM 성능

임베디드 시스템에서 쓰고 지울 수 있는 Flash Memory가 ROM으로 가장 많이 애용

Flash Memory라 함은 ROM이긴 하지만 특별한 control 과정을 거치면 지울 수 있고 그 위에 다시 쓸 수 있다.

언제라도 burning(프로그래밍) 가능한 flash는 임베디드 개발 환경에서 엄청나게 인기가 많음

ROM - Flash memory에도 2가지 타입이 있다. : NOR, NAND (가격 NOR > NAND)

NOR과 NAND 차이는 NOR은 Cell이 병렬로 연결되어 있으며 병렬로 연결되어 있다 보니, Address line과 Data line을 모두 가질 수 있으며 RAM처럼 Byte 단위로 Random Access가 가능하게 합니다. NOR은 XIP를 지원한다. = 즉, SW를 직접 실행할 수 있다.

NAND는 XIP가 안된다. NAND는 Cell이 직렬로 연결되어 있어, 작은 단위로 읽을 수 없고 한 번 읽을때 1개의 page 단위로 읽을 수 있다.

NOR 형은 쓰기와 지우기는 느리지만 읽기가 빠르다, 따라서 대용량 데이터를 저장하는데 한계가 있다.

NAND 형은 읽기는 느리지만 쓰기와 지우기가 빠르다, 따라서 대용량 저장이 가능하다는 장점이 있다.

특이한 정의 : NOR은 코드저장용, NAND는 데이터 저장용

+ flash는 NAND건 NOR건 block 단위로 지울 수 있다.

NAND의 경우 32 또는 64개의 page로 이루어져 있고, NOR도 128KB 단위의 block 단위를 갖는다.

flash memory 업체에서 RAM 까지 손을 뻗쳐 flash memory + RAM을 한꺼번에 한 칩에 집적해 이를 MCP라고 부른다.

MCP에는 여러가지 조합이 가능한데, XIP가 가능한 형태로 System을 구성해야 하는 것이 정답. 그래야 SW를 실행, 동작 가능

예전에는 NOR + PSRAM이 유행. NOR은 XIP가 가능해 코드를 넣고, PSRAM에 데이터를 넣는 형태

현재는 NAND + (DDR) SDRAM 형태에 발맞춘 MCP가 유행 중

NAND는 단지 코드 저장용이고 이런 코드를 SDRAM에 복사해 RAM에서 직접 XIP를 하는 형식으로 발전.

+ NOR Flash의 경우 Start.S를 flash에서 바로 실행할 수 있기에 NOR Flash 내 부트로더 없이 Start.S와 실행하고자 하는 main(.c)만 있으면 실행이 가능한 것으로 이해했다. 그런데, NAND Flash의 경우 flash에서 바로 실행할 수 없으니, 부트로더가 반드시 필요하다고 했는데. NAND에 있는 Start.S와 main.c 모두 실행이 불가능하니, 부트로더가 start.s와 main.c를 실행 가능한 RAM으로 로드하여 실행. 그럼 부트로더는 어디서 실행?

타겟보드에 power on 되자마자 바로 flash type이 NOR인지 NAND인지 확인(보통 타겟보드에 선택하도록 되어 있음).

- 만약 NAND라면, NAND 첫번째 블럭에 있는 부트로더를 CPU 내에 Internal RAM으로 복사. = 부트로더 크기는 Internal RAM보다 크면 안된다. Internal RAM에 부트로더가 올라가면, 이 부트로더는 NAND 두 번째 블록 이후에 있는 프로그램을 SDRAM으로 모두 복사. 마지막으로 Internal RAM에 있는 부트로더는 SDRAM의 시작주소로 점프. 그 이후로는 NOR Flash와 같다.

RAM Memory의 물리적 동작

Memory는 아래와 같이 생겼다.

Address pin과 Data pin으로 구성되며, 나머지는 RD, WR pin으로 구성

메모리마다 처리할 수 있는 양에 따라 address pin의 개수가 틀리다.

1MB까지 처리할 수 있는 녀석의 address pin은 20개(2^20 = 1MB) 있으면 된다.

Data는 0~7까지 8bit로 처리 가능. 이는 한 번에 Data를 담을 수 있는 양이라고 보면 된다.

쓸 때도 1byte, 읽을 때도 1byte 만큼을 한번에 처리할 수 있다.

Memory 동작

0xAB(10101011번지)의 data를 write할 때, WR에 1을 주고 RD에 0을 준다 = Wrtie 명령

그러면 0xAB 번지를 Address pin에 주고, 쓰고 싶은 Data 0x7C(1111100)을 Data pin으로 주면 0xAB번지에 주면 0x7C가 쓰인다.

반대로 읽을 땐 WR에 0을 주고, RD에 1을 준다. 그럼 Data pin으로 0x7C가 튀어 나오게 되는 것이다.

확장 to the CPU - How CPU works

CPU는 여러 논리회로의 집합체.

8bit의 CPU에서 0~7번 pin에 약속된 신호를 주면 CPU는 그에 해당하는 일을 하게 되는 단순한 원리

약속된 전기 신호만 cpu에게 주면 정해진 행동을 수행

CPU 내부는 여러 가지 장치로 구성

제어장치 CU, 연상장치 ALU, CPU 내부 저장 공간인 Register 집합체

CU : 명령어를 해석하여 다른 unit에 동작을 지시하는 일을 수행

(CU와 Decoder로 나눌 수 있는데, Decoder는 명령어를 읽어 해석하는 일, CU는 각종 제어 신호를 발생)

ALU : 산술연산

결과를 임시 저장하는 register file

이런 CPU에 임베디드 시스템에 걸맞게 여러 가지 외부 기능이 더해진 AVR MCU는 다음과 같은 구조

CPU부분은 Program Counter(PC), 32개의 일반적인 register, memory로부터 명령어를 가져와 담아 놓는 instruction register(IR), ALU, 내부 RAM을 가진다. CPU라고 써놓은 부분이 코어다. 나머지는 들러리. CPU block 이외 FLASH, UART, I/O 등 여러가지 기능들의 논리 회로들이 버스를 통해서 연결되어 한 개의 chip 내 implementation 되어 있다. 이런 식의 CPU 이외 여러 가지 기능까지 덧붙여서 한 개의 chip으로 만든 것을 MCU라고 부른다.

Memory로부터 명령어(약속된 일련의 전기적 신호)를 가져오는 일을 pipe lining의 fetch 단계라고 부르는데, 이런 pipe lining이라는 것도 살펴 봐야 한다.

일반적인 CPU 동작의 예(core)dhk Pipe Line

일반적인 CPU 동작 예를 들기 위해, 조금 더 간단해진 CPU모델을 소개

CPU는 최소한의 동작을 위해 CU, ALU 이외 프로그램 카운터, IR, Address Regsister, Data Regsister, ACC 등을 포함하고 있는 일반적인 구조. 아래 그림의 왼쪽이 프로세서(CPU) 부분이고, 오른쪽은 외부에 있으며 프로그램과 데이터를 담고 있는 external memory(RAM, NOR Flash, ROM) 등을 의미

예시) 프로세서 내부의 기억장소인 특정 목적의 레지스터

| Program Counter | CPU가 현재 실행하고 있는 instruction 주소 |

| IR | PC가 가리키는 instruction 주소에서 읽어 온 instruction 담아두는 기억 장소 |

| Address Register | 현재 사용하는 Data를 Access 하기 위한 Data 주소를 가리키는 값을 담아두는 기억 장소 |

| Data Register | Address Register가 가리키는 주소의 실제 값 |

| ACC | 특수한 레지스터로 연산에 사용되는 값을 저장, 연산 결과값을 잠시 저장한다 |

레지스터 이외 기본적인 CPU에서 컴포넌트들은

| Decoder | IR에서 가져온 instruction을 해석해서 CU에 넘김 |

| CU | Central unit, decoder에서 받아온 것을 각종 제어 신호로 변환하여 제어신호 발생 |

| ALU | 산술 연산을 담당하는 unit |

위의 요소들이 모여서 CPU(Processor)를 구성.

word a = 1;

word b = 2;

word c;

word add(void)

{

int temp;

temp = a;

c = a + b;

return;

}

이 예는 CPU가 어떻게 공작하는 지 쉽게 다가서기 위해 만든 예제

일단 a,b,c는 전역변수이므로, 절대 주소를 갖는다.

(전역변수가 절대 주소를 가질 수 있다는 성질은 언제 어디서나 Access 가능하며, 굳이 다른 값으로 바꾸지 않는 한 값을 유지 가능하게 할 수 있는 근거)

a는 0x2000, b는 0x2002, c는 0x2004로 할당

이때, 이 .c code를 compile하면 다음과 같은 assembly가 생성된다고 가정하면 어떨까?

주소 → Assembly

0x1000 → Load 0x2000 / a값을 데이터 레지스터에 로드해서

0x1002 → ADD 0x2002 / 이전에 로드된 a값과 새로 로드하는 b값을 더한 후

0x1003 → STORE 0x2004 / 그 더한 결과를 c의 주소에 저장

1. instruction을 메모리로부터 가져오고 (Fetch)

2. 가져온 instrucion을 해석해서 어떤 일 하는지 알고, register 값들도 확인 (Decoder)

3. Decoding된 instruction 실행 (Execution)

CPU 구조에서 일을 하는 순서는 Fetch → Decode → Execute

다시 말해, 이렇게 sequential하게 3가지 일을 하면, 한 가지 일을 할 때는 다른 2개가 논다.

조금 더 CPU를 효율적으로 움직이게 할 수 있지 않을까 idea에서부터 pipe line이라는 게 생겼다.

= 한번 동작할 때 서로 CPU의 다른 부분을 사용하는 Fetch/Decode/Execution을 한번에 실행하자!

Pipe line 단계가 많아지면 좋아질 것인가?

맞다, Pipe line 많아지면 많을수록 좋아진다.

반면, 너무 많은 stage는 효율성 면에서 성능이 더 좋아지지 않고, 나빠진다.

ARM에서 ARM7의 경우 3단계 pipe line이며, ARM9의 경우 5단계의 pipe line을 거친다.

Pipe line 중 현재 PC(program counter)값은 어디를 가리키고 있을까?

PC는 항상 Fetch 하고 있는 곳을 가리킨다. 고로, 현재 execution하고 있는 곳보다 앞서 간다.

'Embedded System Study > EMBEDDED RECIPES 정리' 카테고리의 다른 글

| 3. Software의 정체와 만들기 (1) | 2025.12.27 |

|---|